Date:2023-04-21 11:28:50 Views:1740

Although TSMC 3nm chips have been mass-produced, but as of yesterday, we have not seen the chip company released related products. Today, this situation has finally been broken.

U.S. chip company Marvell says it has officially launched its data center chip based on TSMC's 3nm process. According to Marvell, the company's industry-first silicon building blocks in the node include a 112G XSR SerDes (serializer/deserializer), Long Reach SerDes, PCIe Gen 6 / CXL 3.0 SerDes and a 240 Tbps parallel chip-to-chip interconnect.

According to Marvell, SerDes and parallel interconnects act as high-speed channels in the chip to exchange data between chips or silicon components within the chiplet. Together with 2.5D and 3D packaging, these technologies will eliminate system-level bottlenecks to advance the most complex semiconductor designs. serDes also helps reduce costs by reducing pins, alignments and board space. Racks in hyperscale data centers can contain tens of thousands of SerDes links.

According to their data, the new parallel chip-to-chip interconnects can achieve aggregated data transfers of up to 240 Tbps, 45% faster than available alternatives for multi-chip packaging applications. In other words, the interconnect transfer rate is equivalent to downloading 10,000 high-definition movies per second, albeit over distances of a few millimeters or less.

Marvell has integrated its SerDes and interconnect technologies into its flagship silicon solutions, including Teralynx switches, PAM4 and coherent DSPs, Alaska Ethernet physical layer (PHY) devices, OCTEON processors, Bravera storage controllers, Brightlane automotive Ethernet chipsets, and custom ASICs. The move to 3nm enables engineers to reduce the cost and power of chips and computing systems while maintaining signal integrity and performance.

According to TSMC, the company's 3nm (N3) process technology will be another full-generation process after the 5nm (N5) process technology, and will be the industry's most advanced process technology with the best PPA and transistor technology at the time of the N3 process technology launch. Compared to the N5 process technology, the N3 process technology will have approximately 70% higher logic density, 10-15% higher speed at the same power consumption, or 25-30% lower power consumption at the same speed.

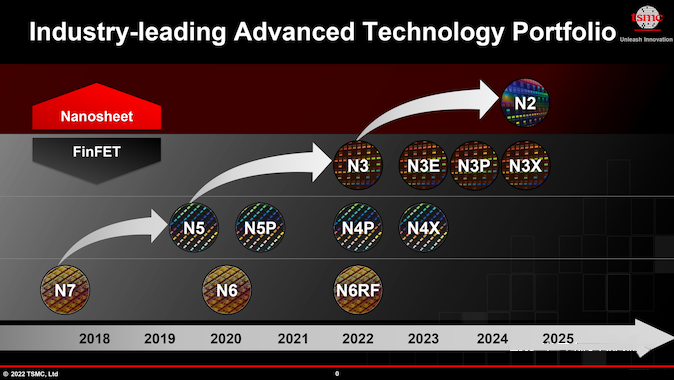

However, the process window (the range of parameters that produce defined results) for N3 is relatively narrow and may not be suitable for all applications in terms of throughput. Also, as manufacturing processes become more complex, they take longer to pathfind, research and develop, so we no longer see an entirely new node emerging every two years from TSMC and other foundries. For N3, TSMC's new node introduction cycle will be extended to about 2.5 years. This means that TSMC will need to offer enhanced versions of N3 to meet the needs of its customers who are still looking for performance per watt improvements and transistor density increases every year or so.

At the 2022 Technology Symposium, TSMC also discussed four N3-derived manufacturing processes (a total of five 3nm-level nodes) - N3E, N3P, N3S and N3X - which will all be available in the next few years. These N3 variants are designed to provide improved process windows, higher performance, higher transistor densities and enhanced voltages for ultra-high performance applications.

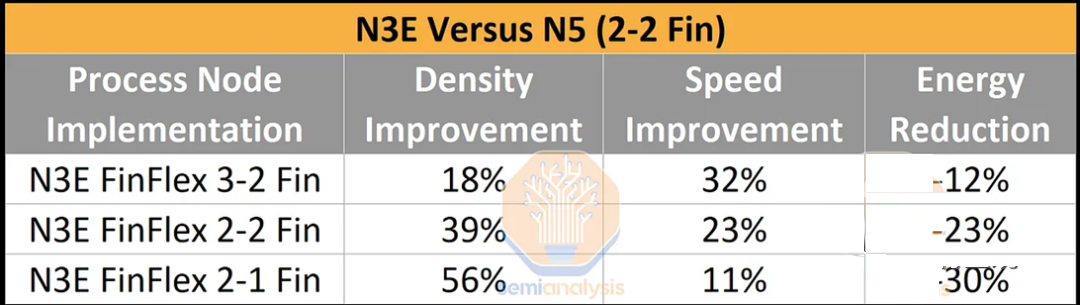

Among them, N3E improves performance, reduces power consumption, and increases process windows, thus increasing brightness. The cost is a slight reduction in logic density for this node. Compared to N5, N3E will have 34% lower power consumption (at the same speed and complexity) or 18% higher performance (at the same power and complexity), and 1.6x higher logic transistor density.

According to reports, TSMC will launch N3P, a performance-enhanced version of its manufacturing process, and N3S, a density-enhanced version of the node, sometime around 2024. However, TSMC is not revealing any more information about these variants at this time. For customers who need ultra-high performance regardless of power and cost, TSMC will offer N3X, essentially a successor to the N4X idea. Again, TSMC did not reveal details about the node, only that it will support high drive currents and voltages.

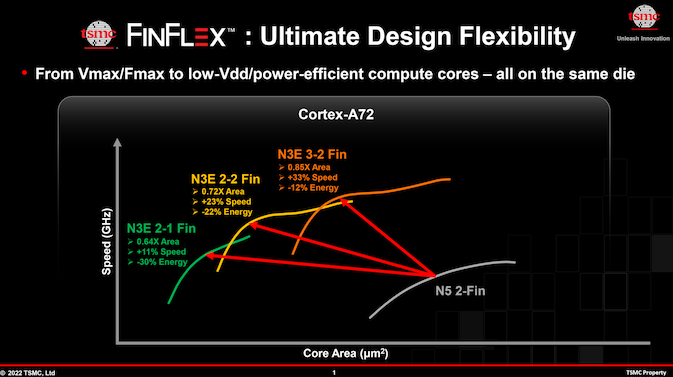

It's worth noting that all of these TSMC technologies will support FinFlex, a TSMC "secret recipe" feature that greatly improves design flexibility and allows chip designers to precisely optimize performance, power and cost. In short, FinFlex allows chip designers to precisely customize their building blocks to achieve higher performance, higher density and lower power consumption.

In real-world applications, TSMC's FinFlex technology will allow chip designers to mix and match different types of standard cells within a block to precisely tailor performance, power consumption and area. For complex architectures like CPU cores, this optimization offers many opportunities to improve core performance while still optimizing chip size.

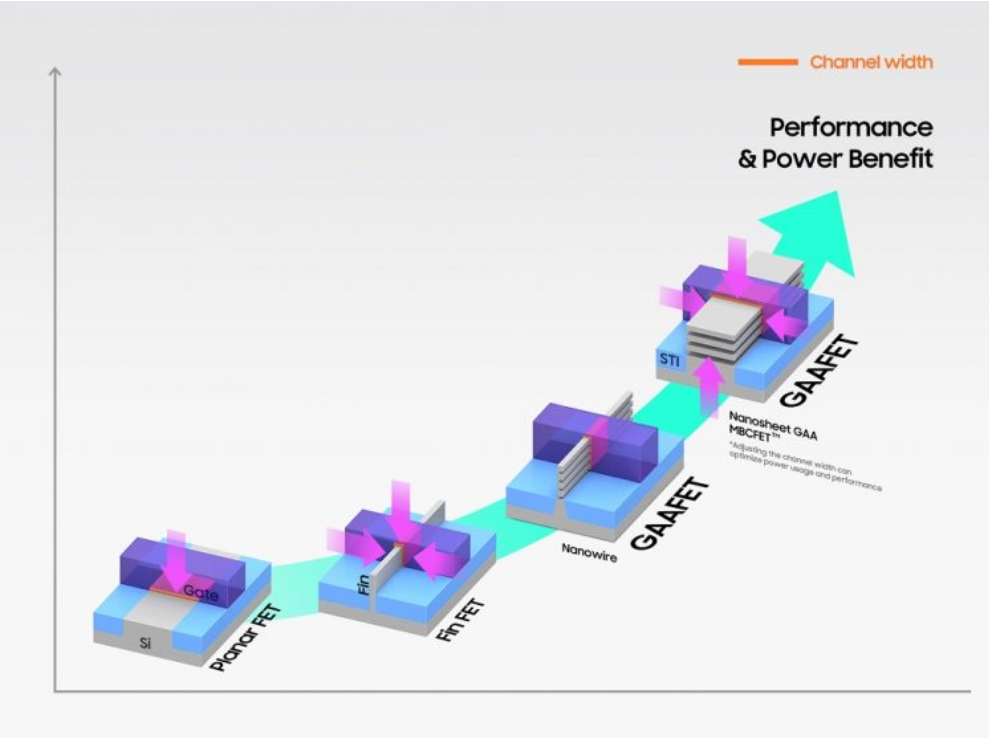

However, we must emphasize that FinFlex is not a substitute for node specialization (performance, density, voltage) because process technologies vary more than library or transistor structures in a single process technology, but FinFlex looks like a good way to optimize performance, power and cost TSMC's N3 node. Ultimately, this technology will bring the flexibility of FinFET-based nodes closer to that of nanosheet/GAAFET-based nodes, which will offer adjustable channel widths for higher performance or lower power consumption.

In fact, long before TSMC announced 3nm mass production, Samsung announced that it had already achieved mass production of 3nm process.

In June 2022, Samsung announced that it had started the initial production of 3nm process nodes using the ring gate (GAA) transistor architecture. The multi-bridge channel FET (MBCFET) used is Samsung's first GAA technology, which breaks through the performance limitations of FinFETs to improve power efficiency by reducing supply voltage levels, while also improving performance by increasing drive current capability. The company is also beginning to use nanosheet transistors with semiconductor chips for high-performance, low-power computing applications, with plans to expand to mobile processors.

Samsung said that utilizing nanosheets with wider channels with the company's proprietary technology enables higher performance and greater power efficiency than GAA technology, which uses nanowires with narrower channels. Using 3nm GAA technology, Samsung will be able to adjust the channel width of the nanosheets to optimize power consumption and performance to meet various customer requirements.

In addition, the design flexibility of GAA is highly conducive to design technology co-optimization (DTCO), which contributes to power, performance, area (PPA) benefits. The first generation 3nm process offers up to 45% lower power, 23% higher performance, and 16% less area compared to the 5nm process, while the second generation 3nm process offers up to 50% lower power, 30% higher performance, and 35% less area.

As mentioned above, unlike TSMC's process, Samsung 3nm uses GAA transistors, which ushers in a new era.

Samsung has been working on 3nm/GAAFET technology since they originally announced the technology in 2019. Samsung's unique GAA transistor technology is multi-bridge channel FET (MBCFET), which is a nanosheet-based implementation. Nanosheet-based FETs are highly customizable, and the width of the nanosheet is a key metric defining power and performance characteristics: the wider the width, the better the performance (at higher power). Thus, transistor designs focused on low power can use smaller nanosheets, while logic requiring higher performance can use wider nanosheets.

In the early days of Samsung's 3nm being released, the industry has been criticizing its yields, but according to industry sources in January, Samsung Electronics Co. on Monday significantly improved its yields for the industry's most advanced 3nm chips produced for fabless customers. The source said Samsung's first-generation 3-nanometer process node production yields reached a "perfect level," but he did not elaborate further.

Previously, Taiwan media reported that TSMC's 3nm process yield was higher than Samsung's at 85%. But South Korean industry sources downplayed the report, saying the figure appeared to be inflated. They said TSMC's production yield is at most 50 percent, considering its mass production and delivery schedule to Apple for the industry's smallest chip.

According to the media, because of the first generation of 3nm, Samsung is heavily invested in the development of the second generation process.

The report disclosed that Samsung's second-generation 3nm GAA process will be in volume production in 2024, and the process will incorporate the MBCFET architecture, which will also improve performance by quite a bit. Although Samsung did not share the statistical differences at the 4nm node, the second-generation 3nm GAA is still expected to reduce power consumption by up to 50%, improve performance by 30%, and reduce wafer area footprint by 35% compared to the company's 5nm process.

Although both Samsung and TSMC have put a lot of thought into 3nm, it seems that everyone is not interested in the first generation of the 3nm process, as seen in past news and announcements from manufacturers. For example, it was once rumored in the market that Apple would be the only customer for TSMC's first-generation 3nm process. However, the American giant has so far failed to announce its 3nm products.

This shows that the first generation of 3nm is not favored by the industry consensus. But the market's pursuit of the process has not yet stopped from what it seems. In addition to these two foundries, Intel will also reportedly launch its 3nm process node at the end of 2023. And they also seem to have their sights set on 2nm.

At that time, Intel's Intel 20A (2nm) will usher in the Angstrom era, utilizing GAA (RibbonFET) transistors and PowerVia technology to improve power retention. Intel's rival TSMC will adopt its GAA at the 2nm node in 2025, putting the former one step ahead as chipmakers hit the miniaturization limit. Add to that Rapidus, a Japanese start-up that will implement a 2nm prototype line in 2025, and Samsung.

For chip companies, how they face the chip design challenge and cost challenge will be their top priority for years to come.