Date:2022-07-15 10:26:23 Views:1131

For FPGA technology development, the acquisition of Xilinx and Altera by AMD and Intel respectively is obviously an important turning point in this history. As FPGA companies change from independent companies to a subdivision of chip giants, their technology development strategies will also change very significantly, and this article will give an outlook on such a strategy development.

First, with the integration of chip giants, FPGAs will be further integrated with traditional chips to take advantage of their programmability, to enable new capabilities of traditional chips, and even to achieve new categories of chips.

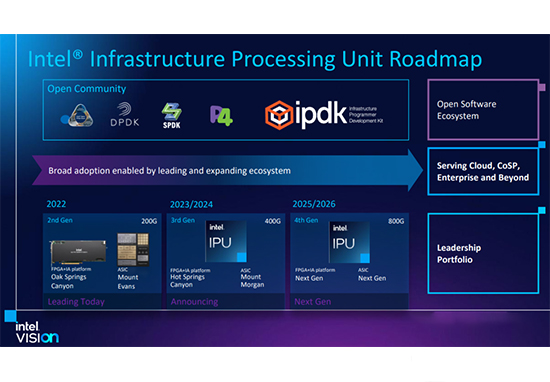

For Intel, an example of such a new category of chips is IPU (infrastructure processing unit, data center processor). Last month, Intel just released its roadmap for the future of IPU, in which we see the future of IPU by 2026. Last month, Intel just released its roadmap for the future of IPUs, in which we see that future IPUs through 2026 will include two versions, a high-performance ASIC-based version and a programmable FPGA-based version (including the Oak Springs Canyon in 2022, the Hot Springs Canyon in 2023/2024, and the version still under planning in 2025/2026). The FPGA-based version of the IPU is in fact an accelerator card that integrates Intel FPGA chips and Intel Xeon CPUs to handle a variety of different networking, storage and security protocols in a flexible manner, thus ensuring maximum programmability without worrying about compatibility issues.

In fact, there have been startups working on FPGA solutions like data center storage and networking for the past few years, but with the entrance of the giant Intel, we think such FPGA+CPU solutions will really become one of the mainstream solutions. The fact that startups are working on related projects and getting funding shows that the technology direction is feasible, and Intel's entry into this market brings ecological resources that startups don't have, and we believe that FPGAs and CPUs will be integrated in a tighter way (e.g. Chiplet) in the coming years, thus truly making flexible programmable IPUs a new category of FPGA-enabled chips. chip category enabled by FPGAs.

AMD is also actively planning to integrate Xilinx FPGAs with AMD CPUs - at AMD's earnings call in May, CEO Lisa Su announced that CPUs with integrated Xilinx AI Engine, i.e. CPUs with powerful AI computing, will be released in 2023. Until today, AI-related calculations have been performed in GPUs or other dedicated acceleration hardware, and Intel's previous efforts to optimize running AI on CPUs have not been massively recognized by the market, as long as they are due to the limited number of CPU computational units. However, since the overall AI task is not only neural network, but also other parts of the program execution running on the CPU, if the CPU and AI acceleration unit can be closely coupled will achieve an increase in the overall performance of the task, which is also estimated to be the original intention of AMD to propose CPUs with integrated FPGA AI engine, and this is also an example of FPGA enabling new chip categories. example.

In summary, with the further popularity of data centers and artificial intelligence and other tasks, Intel and AMD and other giants will consider how to make full use of the flexibility of FPGAs to deal with these markets, and the current situation is not the best solution just to launch FPGA products, but the use of FPGAs and other chips to do integration to launch new chip categories, which will be the future of FPGAs This will be an important market direction for FPGAs in the future. Next, we will also predict where the most critical breakthrough point for FPGAs will be from the technology direction.

As mentioned earlier, as FPGAs need to play a key role in enabling new systems-on-a-chip, we believe that integration and interconnection becomes an important technology key point. The integration and interconnection here includes two levels: first, at the FPGA level, we believe the FPGA chip itself will integrate more and more related IP, thus making the FPGA chip itself more functional and efficient; the other level is the integration of the FPGA and other chips in the system, and we believe advanced packaging technologies such as chiplet and related interconnection technologies will be the core.

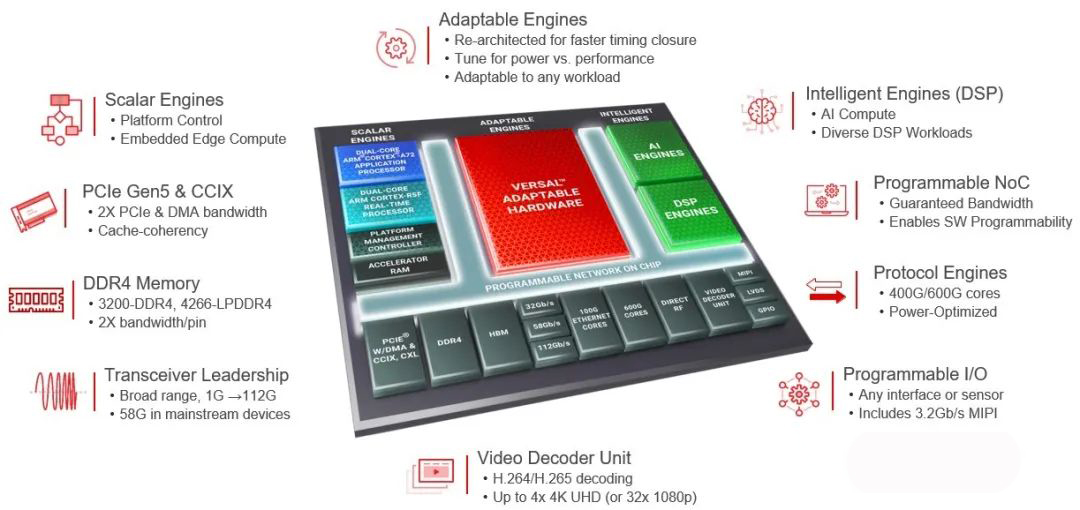

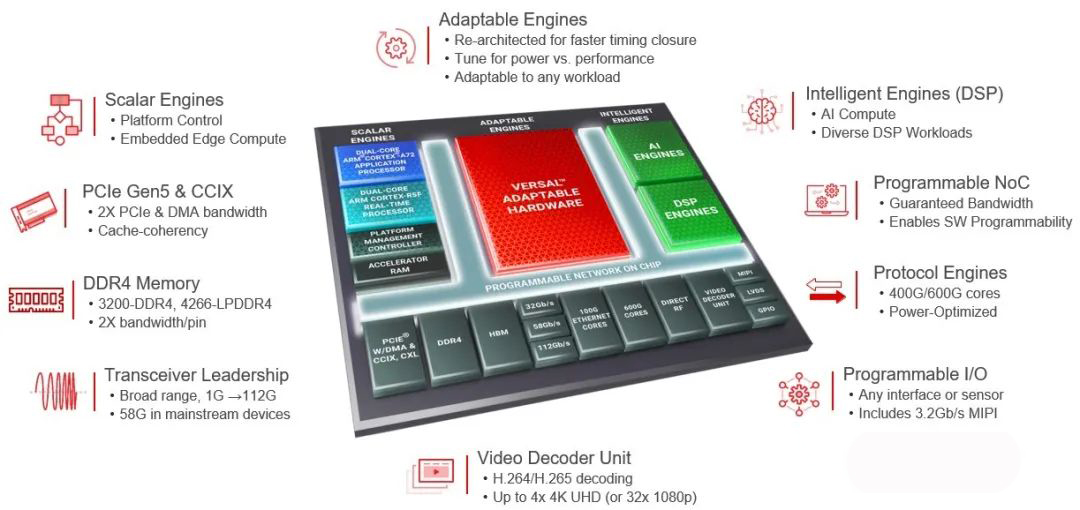

First, at the FPGA chip level, FPGAs provide flexibility, but for general-purpose modules (such as processors, etc.) efficiency is low, so the integration of hard IP on FPGA chips to meet the needs of both efficiency and flexibility will continue to be the mainstream thinking, and the number of integrated IP will increase in the future. AMD/Xilinx is a pioneer in this area, and its roadmap for the Versal product line shows that more and more hard IPs will be integrated on the chip, and Intel's FPGAs will have a similar design in this regard. By integrating these hard IPs, FPGAs will be able to provide more powerful functionality. For Xilinx, its most critical IP is AI-related DSP, and we also see some new IP, such as Direct RF, which can directly support RF applications through ultra-high speed digital-to-analog conversion, and is expected to be combined with FPGAs to meet the needs of various wireless communications, so that true software radio can be achieved, thus opening up new application scenarios for FPGAs. This will enable true software radio, thus opening up new application scenarios for FPGAs. Therefore, by integrating more and more hard IP on FPGA chips, it will become an important technology path to make FPGAs more powerful and enter new application scenarios.

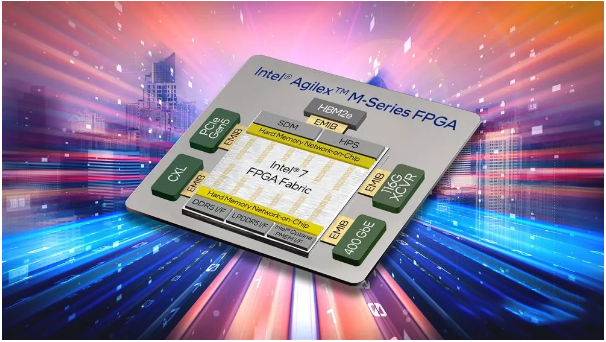

The second level is the integration and interconnection of FPGAs and other chips at the system level. We believe that such integration will be the key for FPGAs to enable new chip systems and categories, and combined with more hard IP integration on FPGA chips as mentioned before, we believe that eventually more and more powerful FPGAs can enable more and more new chip categories and open up the market. At this level, we believe the most critical technology path is to achieve flexible and customizable heterogeneous integration in the form of advanced packaging, and complemented by innovative interconnect technologies. In this regard, Intel has earlier announced the use of advanced packaging technology (EMIB) to integrate FPGAs and high-speed transceivers (for data center scalable interconnects) and DRAM, etc. all in one package. At the HOTCHIPS conference later this year, Intel also has a presentation on using heterogeneous integration to enable innovative RF applications. The main advantage of using heterogeneous integration is its flexibility, such as the ability to integrate with different types and sizes of chips depending on the user's needs, to achieve a compromise between maximizing performance, cost and customizability.

Similarly, AMD's plan to integrate the Xilinx FGPA with the CPU, although no clear technical specifications have been released, we believe that based on AMD's previous investments in chiplets and AMD's previous patents, there is a high probability that chiplet technology will be used.

As the scale of such integration grows, the need for interconnection grows, otherwise the interconnection may become a bottleneck in multi-chip systems. Interconnects need to be able to provide not only high bandwidth, but also support for important system-level functions, such as cache and memory coherency. Currently, Intel and AMD FPGAs support the CXL protocol, and we believe that increasingly complex and high-speed interconnects between chips will become a key technology as FPGAs and processors and other chips become more integrated.

In addition to hardware, how to make the most efficient use of FPGAs in real-world tasks is also a critical issue. As FPGAs and other chips (e.g. CPUs) are tightly integrated to form a heterogeneous chip system, how to ensure that software can take full advantage of FPGAs and avoid bottlenecks in scheduling is a very complex but important issue. This is a very challenging problem because the programming models of FPGAs and other parts of the system (e.g. CPUs) can be very different, so how to ensure that the software can correctly partition tasks (i.e. assign tasks suitable for FPGAs to FPGAs and tasks suitable for other processors to the corresponding processors), handle scheduling and memory management rationally, and be available in a more user-friendly form for software engineers to use, is a lot of engineering. These are tasks that are quite different from traditional FPGA software (i.e., mainly for front-end and back-end logic synthesis tasks).

Both Intel and AMD are actively investing in this area. For example, the IPU roadmap released by Intel, open and flexible software ecosystem is an important area of investment for Intel, and with the corresponding Intel just announced recently to acquire cross-platform heterogeneous chip software compiler company Codeplay, this move is also considered by the industry in the next generation of FPGA software investment. At the same time, AMD also said in the May earnings conference to invest heavily in the software field, obviously here also includes FPGA-related software development. We believe that as FPGAs become an important part of the new system-on-a-chip, the corresponding software ecosystem must also keep up, thus making such a new paradigm of FPGA systems truly enter the mainstream.